## Czech Technical University in Prague Faculty of Electrical Engineering

# **Doctoral Thesis**

August 2023

Ing. Pavel Skarolek

Czech Technical University in Prague

Faculty of Electrical Engineering Department of Electrical Drives and Traction

## IMPROVING THE ELECTRIC VEHICLE CONVERTER PERFOMANCE USING NEW SEMICONDUCTOR COMPONENTS

**Doctoral Thesis**

Ing. Pavel Skarolek

Prague, August 2023

Ph.D. Programme: Electrical Engineering and Information Technology, P2612 Branch of study: Electric Machines, Apparatus and Drives, 2642V004

Supervisor: prof. Ing. Jiří Lettl, CSc.

## Declaration

I hereby declare that I have written my doctoral thesis on my own and I have used only the literature listed at the end of the doctoral thesis in the references.

### Abstract

Semiconductor devices based on gallium nitride (GaN) are becoming to be used in power converters to increase the power density and improve the efficiency. Using the new technology of fast switching transistors in DC/DC converters and inverters brings new problems to be analyzed. The thesis covers complex area from GaN drivers design, cooling system, to minimizing losses in switch-on and switch-off state. Optimization of converter control algorithm achieved decrease of conduction losses caused by the currentcollapse phenomenon. Additional optimum dead-time tracking algorithm decreased the losses caused by the transistor's reverse conduction region.

### Keywords

Gallium nitride, GaN HEMT, gate driver, voltage source inverter, current-collapse, dead-time

### Abstrakt

Součástky na bázi nitridu galia (GaN) pronikají do oblasti výkonových měničů a umožňují tak dosahovat vyšší hustoty výkonu a vyšší účinnosti. Použití nové technologie rychlých spínacích součástek v DC/DC měničích a střídačích přináší nové problémy, které je potřeba analyzovat. Práce se zabývá komplexní problematikou od návrhu driverů pro GaN tranzistory, jejich chlazení a snižováním ztrát v sepnutém a vypnutém stavu. Díky optimalizaci algoritmu řízení bylo možno dosáhnout snížení ztrát v propustném směru způsobených jevem "current-collapse". Doplněním sledovacího algoritmu pro nalezení optimálního proměnného "dead-time", byly sníženy ztráty způsobené vedením tranzistoru v závěrném směru.

### Klíčová slova

Nitrid galia, GaN HEMT, budič gate, napěťový střídač, current-collapse, dead-time

## List of Content

| 1 | Introd | luction                                              | 1  |

|---|--------|------------------------------------------------------|----|

|   | 1.1 Т  | The State of Art                                     | 3  |

|   | 1.1.1  | Hybrid Electric Vehicles                             | 3  |

|   | 1.1.2  | Battery Electric Vehicles                            | 3  |

|   | 1.1.3  | Power Converters in Electric Vehicle Tractive System | 8  |

|   | 1.1.4  | Semiconductor Devices                                | 9  |

|   | 1.2 N  | Activation                                           | 16 |

|   | 1.3 T  | hesis Objectives                                     | 17 |

| 2 | Curre  | nt Limiting Driver for GaN Transistor                | 18 |

|   | 2.1 0  | Gallium Nitride Basis                                | 18 |

|   | 2.1.1  | No Reverse Recovery                                  | 18 |

|   | 2.1.2  | Gate Driving Requirements                            | 19 |

|   | 2.2 0  | GaN Driver Design Requirements                       | 20 |

|   | 2.2.1  | Current Measuring                                    | 20 |

|   | 2.2.2  | Safe Turn-Off Over-Current                           | 21 |

|   | 2.2.3  | PCB Design                                           | 22 |

|   | 2.3 E  | Designed Prototype                                   | 23 |

|   | 2.3.1  | Proposed Driver Schematic Diagram                    | 23 |

|   | 2.3.2  | Testing the Prototype                                | 25 |

|   | 2.4 D  | Discussion                                           | 28 |

| 3 | Cooli  | ng Possibilities of GaN Semiconductors               | 29 |

|   | 3.1 D  | Description of Cooling Options                       | 29 |

|   | 3.1.1  | Bottom Side Cooled GaN on IMS Board                  | 29 |

|   | 3.1.2  | Top Side Cooled GaN                                  | 30 |

|   | 3.1.3  | Bottom Side Cooled GaN on FR4 Board                  | 30 |

|   | 3.1.4  | Thermal Resistance Estimation                        | 31 |

|   | 3.2 E  | Experimental Setup                                   | 32 |

|   | 3.2.1  | GaN on IMS Board                                     | 32 |

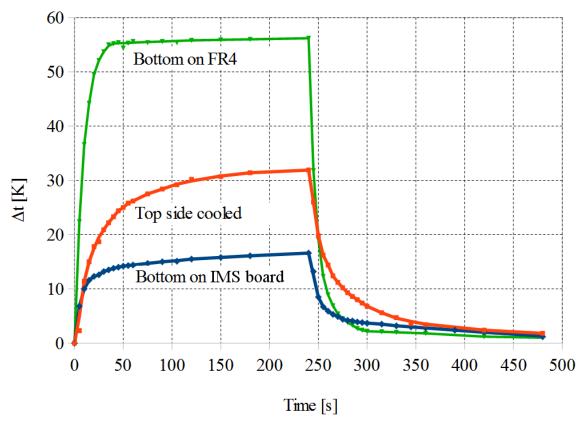

|   | 3.3 E  | Experimental Results                                 | 34 |

|   | 3.3.1  | Driver Verification                                  | 34 |

|   | 3.3.2  | Cooling Options Comparison                           | 36 |

|   | 3.4 D  | Discussion                                           | 38 |

|   |        |                                                      |    |

| 4 Ga    | N Transistor Switch-On Loss Reduction                         | 39  |

|---------|---------------------------------------------------------------|-----|

| 4.1     | Theoretical Analysis                                          | 40  |

| 4.1     | .1 Space-Vector Modulation with Minimum Pulse Width Limitatio | n42 |

| 4.1     | .2 Drive Losses Analysis                                      | 44  |

| 4.1     | .3 PMSM Control Strategy                                      | 44  |

| 4.2     | Experimental Results                                          | 46  |

| 4.2     | .1 Experimental Setup                                         | 46  |

| 4.2     | .2 Pulse Width Limiting                                       | 47  |

| 4.2     | .3 Current-Collapse Loss Minimization                         | 48  |

| 4.3     | Discussion                                                    | 53  |

| 5 Ga    | N Transistor Switch-Off Loss Reduction                        | 55  |

| 5.1     | Theoretical Analysis                                          | 55  |

| 5.1     | .1 Dead-Time Generation                                       | 56  |

| 5.1     | .2 Reverse Conduction Loss                                    | 58  |

| 5.1     | .3 Drive Controller                                           | 59  |

| 5.1     | .4 Tracking Algorithm                                         | 61  |

| 5.2     | Experimental Results                                          | 61  |

| 5.2     | .1 Experimental Setup                                         | 62  |

| 5.2     | .2 Current Controllers' Output Change with Dead-Time          | 63  |

| 5.2     | .3 Tracking Algorithm                                         | 65  |

| 5.2     | .4 Dead-Time Loss Minimization                                | 66  |

| 5.2     | .5 Comparison with Other Methods Mentioned in the Literature  | 67  |

| 5.3     | Discussion                                                    | 67  |

| 6 Ga    | N Bridgeless Converter Variable Dead-Time                     | 69  |

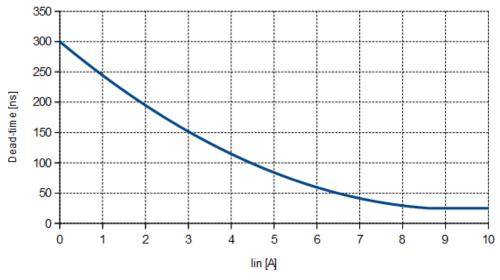

| 6.1     | On-Line Variable Dead-Time                                    | 69  |

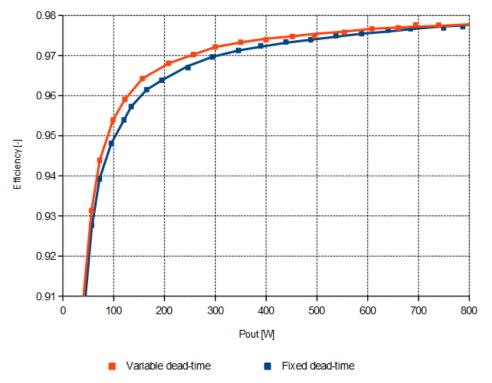

| 6.2     | Experiment                                                    | 71  |

| 6.3     | Discussion                                                    | 73  |

| 7 Co    | onclusions                                                    | 74  |

| 7.1     | Fulfilment of the Thesis Objectives                           | 74  |

| 7.2     | Future Work                                                   | 75  |

| Referen | ces                                                           | 76  |

| Author' | s Publications Related to the Thesis                          | 82  |

| Author' | s Other Publications                                          | 84  |

## **List of Figures**

| Fig. 1 Global EV sales [6]                                                                                                |   |

|---------------------------------------------------------------------------------------------------------------------------|---|

| Fig. 2 Parallel hybrid vehicle topology [12]                                                                              |   |

| Fig. 3 Energy density comparison for lead, nickel and lithium-based cells [13]                                            | 4 |

| Fig. 4 Discharge curve of lithium-based cell [14]                                                                         |   |

| Fig. 5 Example of 500 Wh battery pack of lithium cells                                                                    |   |

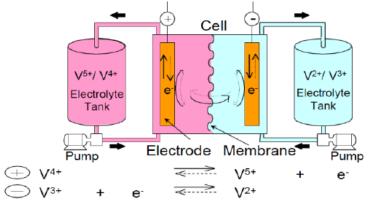

| Fig. 6 Vanadium redox flow cell principle [20]                                                                            | 6 |

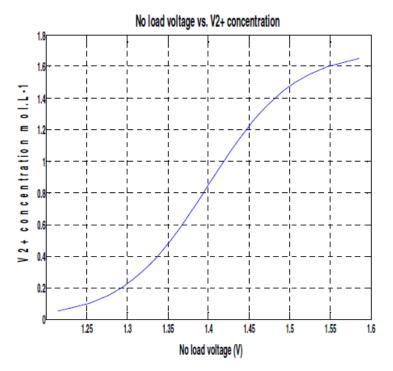

| Fig. 7 Vanadium redox flow cell voltage [20]                                                                              | 6 |

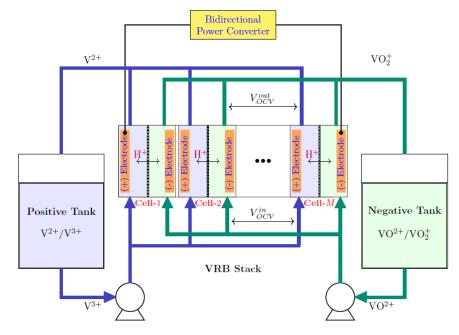

| Fig. 8 Multiple cell vanadium redox flow battery [21]                                                                     | 7 |

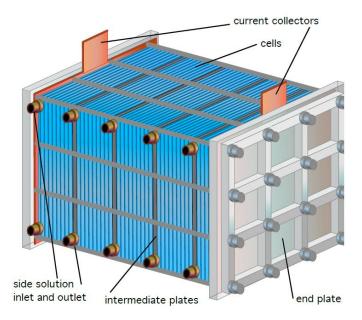

| Fig. 9 Vanadium redox flow battery stack [16]                                                                             | 7 |

| Fig. 10 EV power converters [22]                                                                                          |   |

| Fig. 11 Power semiconductors typical application for power and switching frequ                                            |   |

| Fig. 12 Classic MOSFET structure <i>R</i> <sub>DSon</sub> components [23]                                                 |   |

| Fig. 13 CoolMOS structure in turn-on (left) and turn-off state (right) [23]                                               |   |

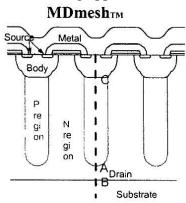

| Fig. 14 MDmesh structure [26]                                                                                             |   |

| Fig. 15 IGBT structure in turn-on (left) and turn-off (right) [23]                                                        |   |

| Fig. 16 SiC MOSFET classic structure (left), trench structure (center), proposed asymmetric trench structure (right) [31] | - |

| Fig. 17 External Schottky diode in SiC transistor [32]                                                                    |   |

| Fig. 18 Depletion mode GaN on Si as a part of the cascade [7]                                                             |   |

| Fig. 19 GaN on Si GIT structure [33]                                                                                      |   |

| Fig. 20 Output capacitance dependence on V <sub>DS</sub> [8]                                                              |   |

| Fig. 21 GaN-based 650 V 60 A transistors                                                                                  |   |

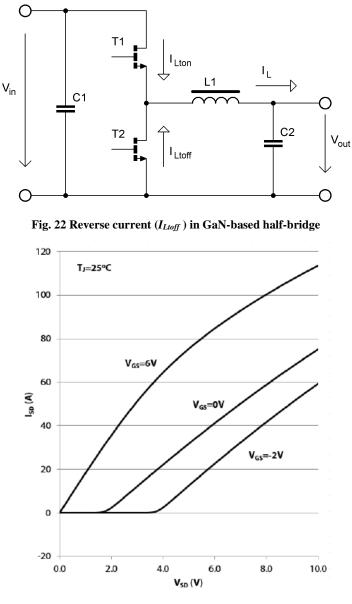

| Fig. 22 Reverse current ( <i>I</i> <sub>Ltoff</sub> ) in GaN-based half-bridge                                            |   |

| Fig. 23 Reverse conduction region [34]                                                                                    |   |

| Fig. 24 Forward conduction region [34]                                                                                    |   |

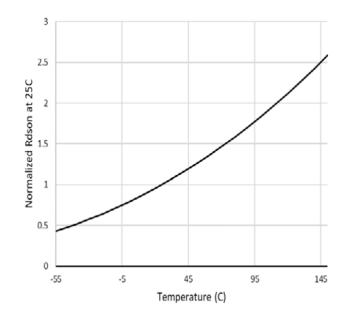

| Fig. 25 <i>R</i> <sub>DSon</sub> temperature dependency [34]                                                              |   |

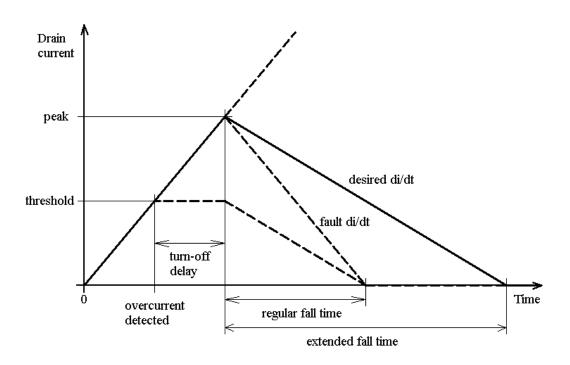

| Fig. 26 Fall time extending                                                                                               |   |

| Fig. 27 Current loop minimizing example                                                                                   |   |

| Fig. 28 Block diagram of the current limiting driver                                                                      |   |

| Fig. 29 Circuit diagram of the current limiting driver                                                                    |   |

|                                                                                                                           |   |

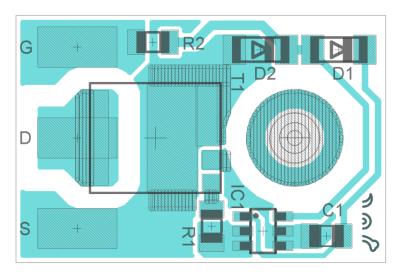

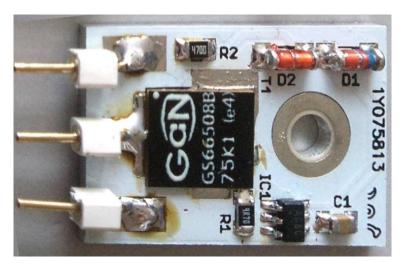

| Fig. 30 PCB prototype25                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 31 Simplified circuit for testing the over-current protection reaction on short circuiting of the converter output                                                                                                           |

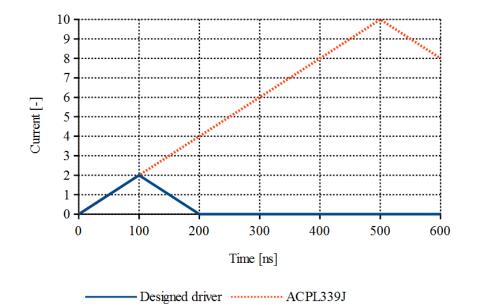

| Fig. 32 Comparison of the current protection response times reckoned with relative current values assuming both drivers used in the same circuit shown in Figure 4. The ACPL339J graph is drawn on base of the data given in [40] |

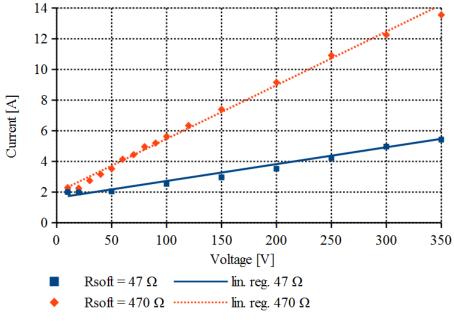

| Fig. 33 Peak current depending on voltage and R <sub>soft</sub> 27                                                                                                                                                                |

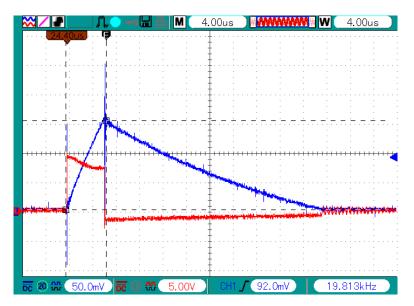

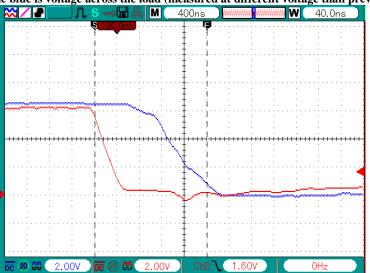

| Fig. 34 Inductive load turn-off with the over-current protection set to 3 A, blue is current as 50mV/A and red is voltage across the load according to the Fig. 3127                                                              |

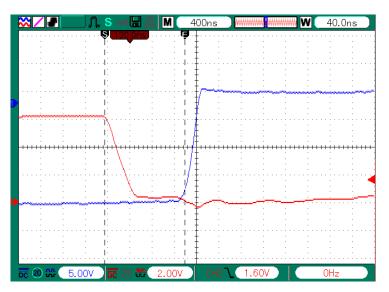

| Fig. 35 Over current detection turn-off delay. Red line is the output of a comparator that detects the over current and the blue is voltage across the load (measured at different voltage than previous picture)                 |

| Fig. 36 Slow gate discharge after over-current detected. The blue is voltage at the gate and red comparator output to show when the over-current was detected                                                                     |

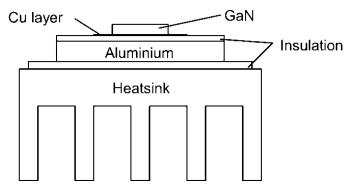

| Fig. 37 Bottom side cooled transistor placed on IMS board                                                                                                                                                                         |

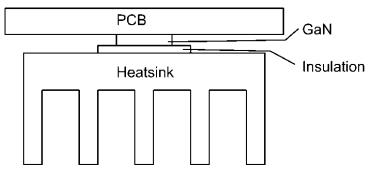

| Fig. 38 Top side cooled transistor with heatsink                                                                                                                                                                                  |

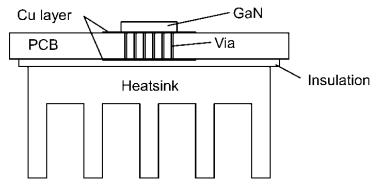

| Fig. 39 Bottom side cooled transistor placed on FR4 board                                                                                                                                                                         |

| Fig. 40 Gate current buffer schematic diagram                                                                                                                                                                                     |

| Fig. 41 IMS board layout                                                                                                                                                                                                          |

| Fig. 42 Finished IMS board                                                                                                                                                                                                        |

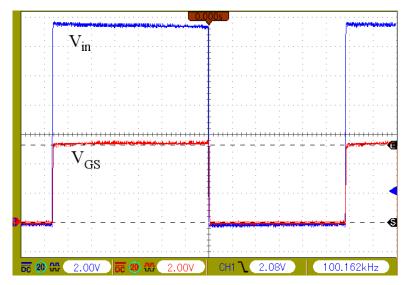

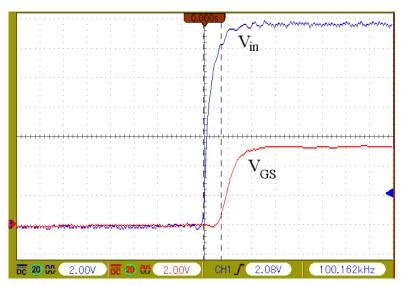

| Fig. 43 Input voltage $V_{in}$ on the current buffer gate terminal and $V_{GS}$ measured on the GaN transistor 2 V/div, 1 $\mu$ s/div                                                                                             |

| Fig. 44 Measured turn-on delay 15 ns                                                                                                                                                                                              |

| Fig. 45 Measured turn-off delay 35 ns                                                                                                                                                                                             |

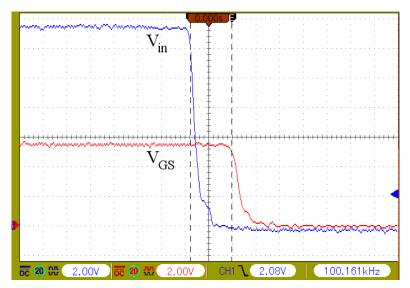

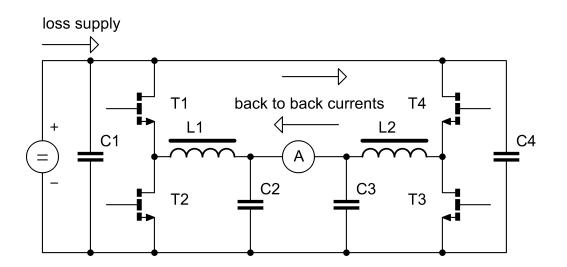

| Fig. 46 Two converters in back-to-back configuration                                                                                                                                                                              |

| Fig. 47 Finished experimental converters: top side cooled variant (on the left), bottom side cooled on IMS board (in the middle), and bottom on FR4 board (on the right)37                                                        |

| Fig. 48 Cooling options comparison                                                                                                                                                                                                |

| Fig. 49 Three-phase two-level GaN voltage-source inverter                                                                                                                                                                         |

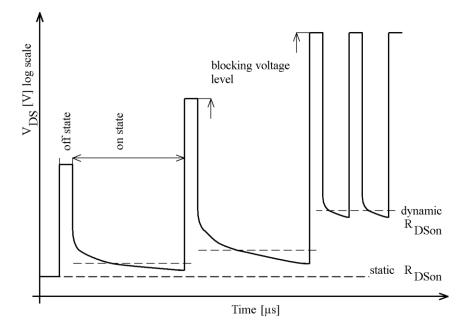

| Fig. 50 Current-collapse effect on the GaN on-state resistance                                                                                                                                                                    |

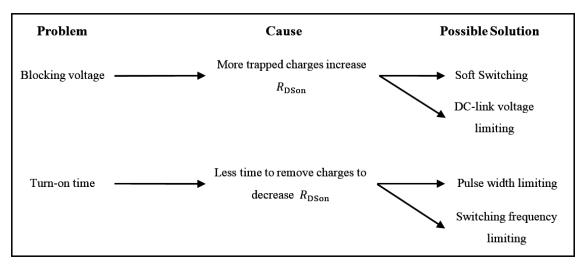

| Fig. 51 Problems connected with current collapse, their causes, and possible solutions42                                                                                                                                          |

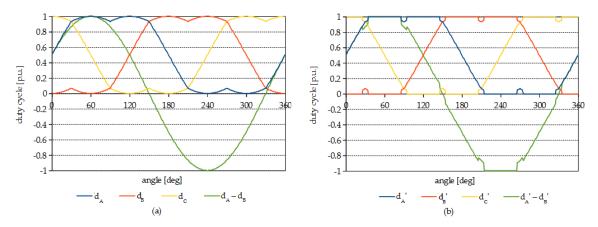

| Fig. 52 SVPWM in (a) linear mode, (b) deformed SVPWM with 5 % pulse width limitation                                                                                                                                              |

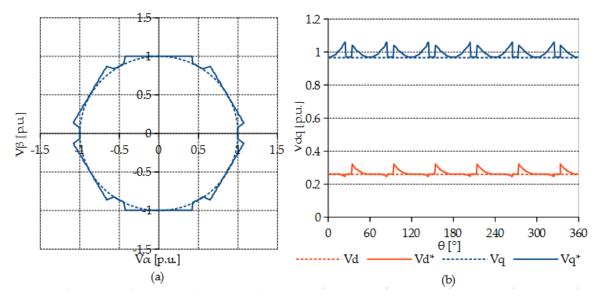

| Fig. 53 Deformation of the voltage vector caused by the pulse width limiting set to 5 % of the duty cycle at a load angle of 15° (PMSM from the experimental part is considered)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

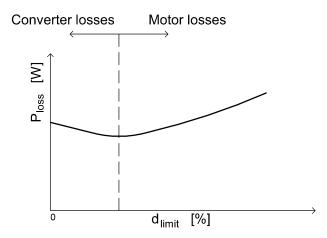

| Fig. 54 Electric drive loss distribution based on the duty cycle pulse width limit value 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

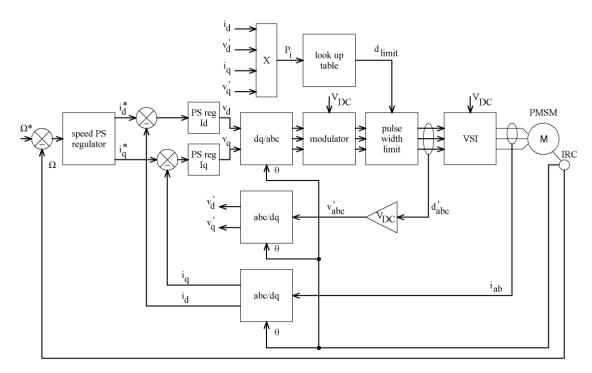

| Fig. 55 PMSM control scheme with added LUT-based pulse width limiting block 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

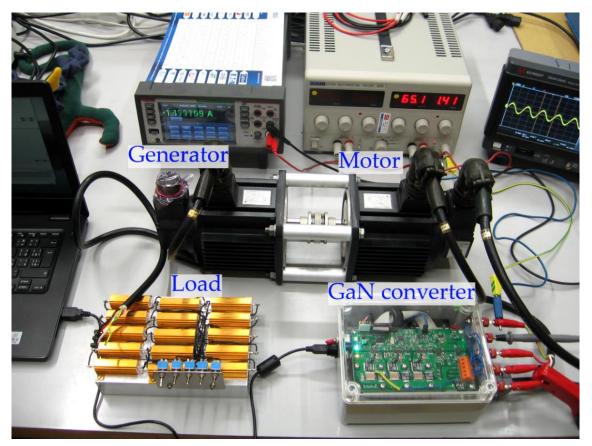

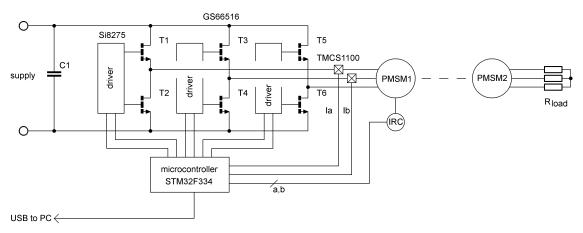

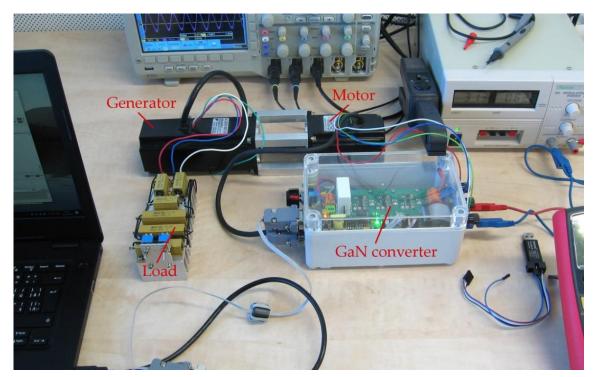

| Fig. 56 Experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Fig. 57 Simplified schematic diagram of the experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

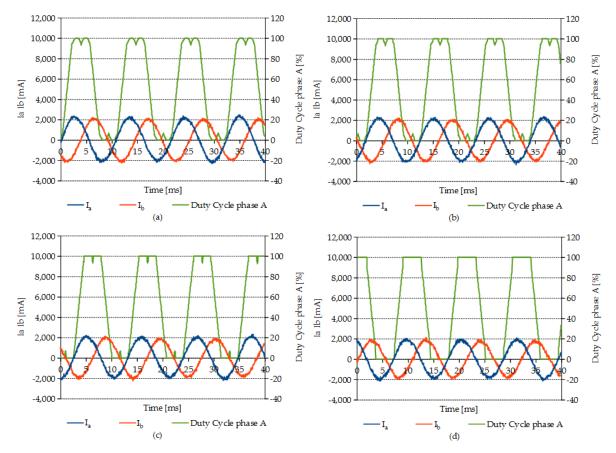

| Fig. 58 Modulation with: (a) no pulse width limited, (b) with the limiting value 5 %, and (c) with the limiting value 10 % of the nominal duty cycle. Reference speed 2000 RPM, 100 V DC-link voltage, load resistance $R_{load} = 100 \Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

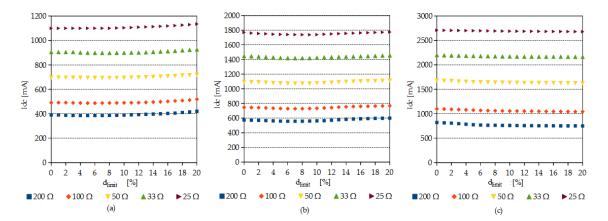

| Fig. 59. Input DC-link current measured for different loads at (a) 1500 RPM, (b) 2000 RPM, and (c) 2500 RPM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

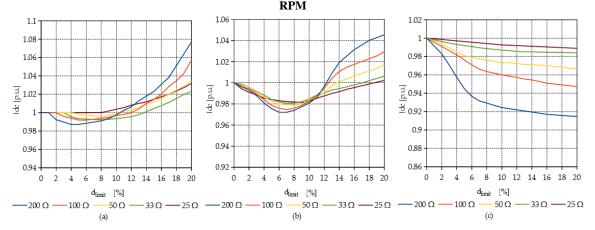

| Fig. 60 Relative input DC-link current measured for different loads at (a) 1500 RPM, (b) 2000 RPM, and (c) 2500 RPM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

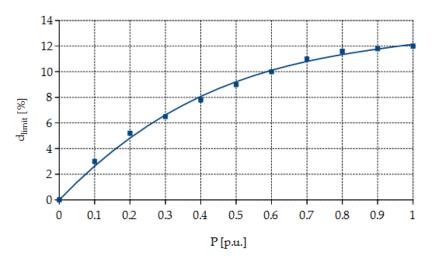

| Fig. 61 Third-order polynomial function fitted to the measured data (limiting duty-cycle as a function of the inverter output power)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

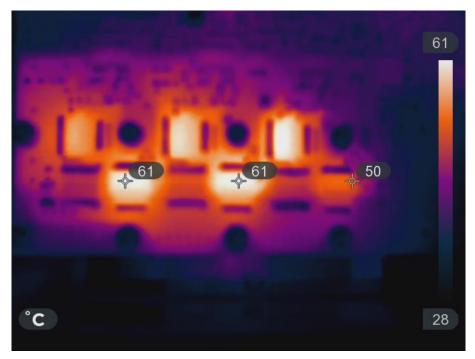

| Fig. 62 Infrared camera measurement at 2000 RPM and $R_{load} = 25 \Omega$ without pulse width limitation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

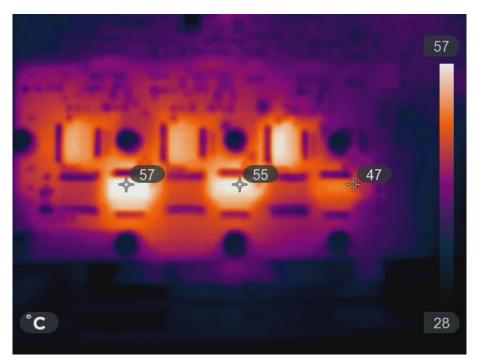

| Fig. 63 Infrared camera measurement at 2000 RPM and $R_{load} = 25 \Omega$ with LUT-based pulse width limitation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| pulse width limitation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

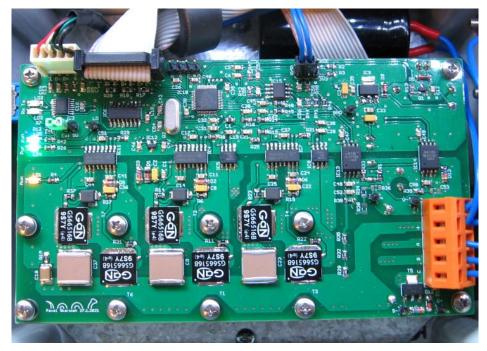

| pulse width limitation52Fig. 64 Detail of the inverter board53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

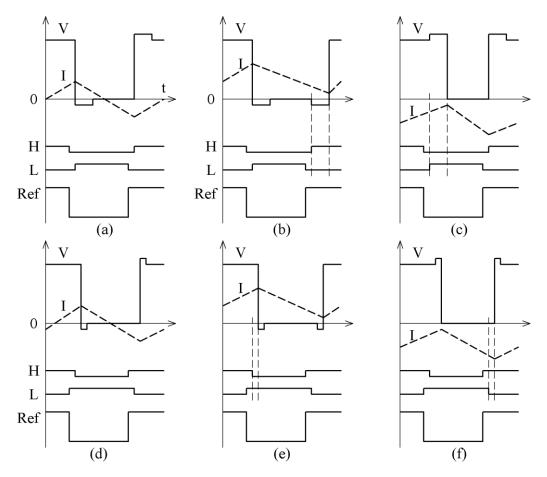

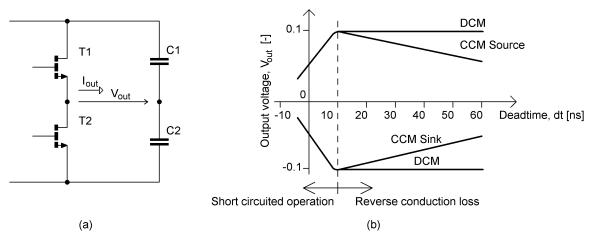

| pulse width limitation52Fig. 64 Detail of the inverter board53Fig. 65 A typical GaN-based half-bridge configuration56Fig. 66 Output duty cycle for (a) discontinuous conduction mode (DCM) positive dead-<br>time, (b) continuous conduction mode (CCM) current source positive dead-time, (c) CCM<br>current sink positive dead-time, (d) DCM negative dead-time, (e) CCM current source                                                                                                                                                                                                                                                                                                                      |

| pulse width limitation52Fig. 64 Detail of the inverter board53Fig. 65 A typical GaN-based half-bridge configuration56Fig. 66 Output duty cycle for (a) discontinuous conduction mode (DCM) positive dead-<br>time, (b) continuous conduction mode (CCM) current source positive dead-time, (c) CCM<br>current sink positive dead-time, (d) DCM negative dead-time, (e) CCM current source<br>negative dead-time, and (f) CCM current sink negative dead-time                                                                                                                                                                                                                                                   |

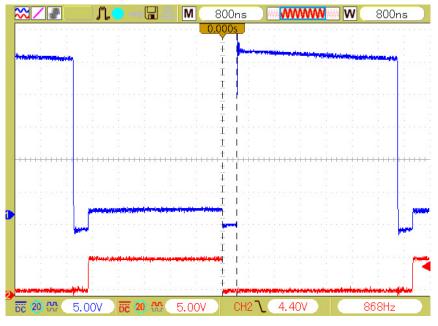

| pulse width limitation52Fig. 64 Detail of the inverter board53Fig. 65 A typical GaN-based half-bridge configuration56Fig. 66 Output duty cycle for (a) discontinuous conduction mode (DCM) positive dead-<br>time, (b) continuous conduction mode (CCM) current source positive dead-time, (c) CCM<br>current sink positive dead-time, (d) DCM negative dead-time, (e) CCM current source<br>negative dead-time, and (f) CCM current sink negative dead-timeFig. 67 Half-bridge output voltage (blue) and low-side transistor gate signal (red)58Fig. 68 Output voltage dependence on dead-time:<br>(a) virtual DC-link neutral point, (b)                                                                     |

| pulse width limitation52Fig. 64 Detail of the inverter board53Fig. 65 A typical GaN-based half-bridge configuration56Fig. 66 Output duty cycle for (a) discontinuous conduction mode (DCM) positive dead-<br>time, (b) continuous conduction mode (CCM) current source positive dead-time, (c) CCM<br>current sink positive dead-time, (d) DCM negative dead-time, (e) CCM current source<br>negative dead-time, and (f) CCM current sink negative dead-time.57Fig. 67 Half-bridge output voltage (blue) and low-side transistor gate signal (red)58Fig. 68 Output voltage dependence on dead-time: (a) virtual DC-link neutral point, (b)<br>dependence of output voltage on dead-time and modes of operation |

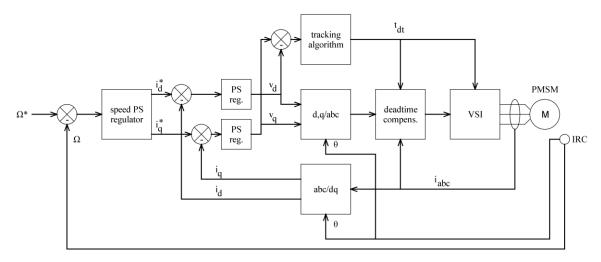

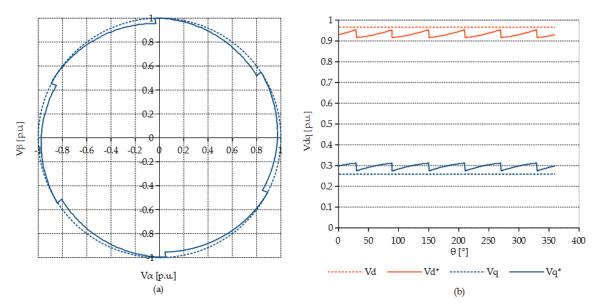

| pulse width limitation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

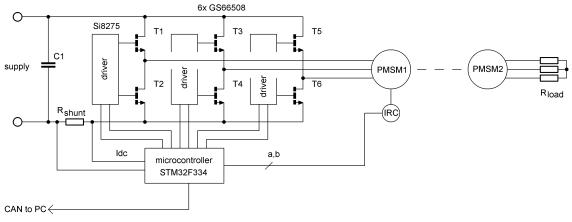

| Fig. 73 Dependence of current controllers' outputs on the set dead-time for different speed references; mechanical load created by PMSM with a variable resistance $R_{load}$ in the armature: (a) <i>d</i> -axis current controller, $R_{load} = 187 \Omega$ ; (b) <i>q</i> -axis current controller, $R_{load} = 187 \Omega$ ; (c) <i>d</i> -axis current controller, $R_{load} = 73 \Omega$ ; and (d) <i>q</i> -axis current controller, $R_{load} = 73 \Omega$ |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 74 More detailed depiction of curves from Fig. 73: (a) <i>d</i> -axis current controller, $R_{load}$ = 187 $\Omega$ ; (b) <i>q</i> -axis current controller, $R_{load}$ = 187 $\Omega$ ; (c) <i>d</i> -axis current controller, $R_{load}$ = 73 $\Omega$ ; and (d) <i>q</i> -axis current controller, $R_{load}$ = 73 $\Omega$                                                                                                                                |

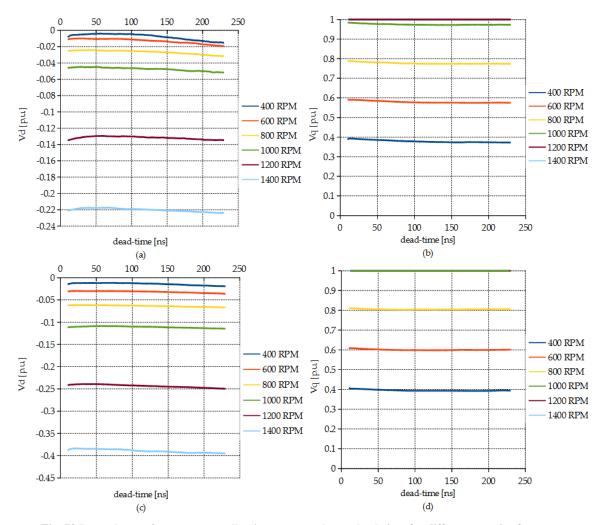

| Fig. 75 Tracking algorithm searching for an optimum dead-time for (a) 800 RPM, $R_{load} = 187 \Omega$ ; (b) 1200 RPM, $R_{load} = 187 \Omega$ ; (c) 800 RPM, $R_{load} = 73 \Omega$ ; and (d) 1200 RPM, $R_{load} = 73 \Omega$                                                                                                                                                                                                                                    |

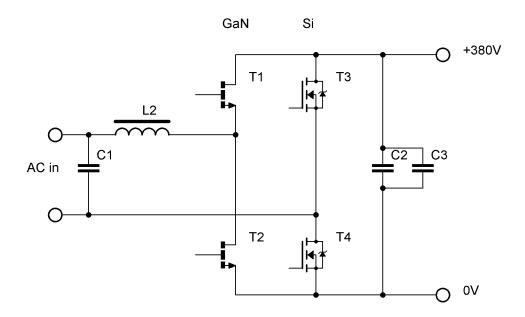

| Fig. 76 GaN-based bridgeless PFC converter69                                                                                                                                                                                                                                                                                                                                                                                                                       |

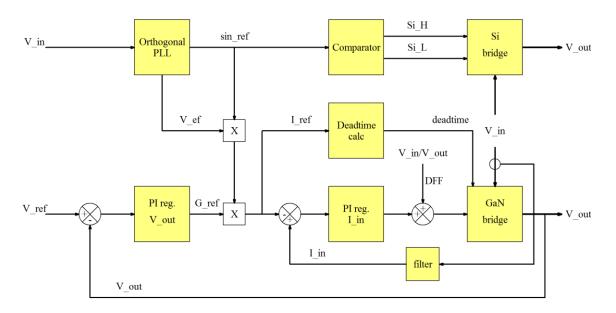

| Fig. 77 PFC control circuit70                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Fig. 78 Set dead-time dependence on half-bridge input current71                                                                                                                                                                                                                                                                                                                                                                                                    |

| Fig. 79 Experimental setup72                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Fig. 80 Efficiency curve with variable and fixed dead-time                                                                                                                                                                                                                                                                                                                                                                                                         |

## **List of Tables**

| Tab. 1 SiC to IGBT converter efficiency comparison [30]                                                                                                          | 12 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tab. 2 Si, SiC and GaN transistor parameter comparison [8]                                                                                                       | 15 |

| Tab. 3 Gate control logic                                                                                                                                        | 21 |

| Tab. 4 Current protection response time                                                                                                                          | 25 |

| Tab. 5 Estimated thermal resistances                                                                                                                             | 31 |

| Tab. 6 Motor and generator parameters                                                                                                                            | 47 |

| Tab. 7 DC-link current measurement for various operating points                                                                                                  | 51 |

| Tab. 8 Output duty cycle in CCM                                                                                                                                  | 58 |

| Tab. 9 Motor and generator parameters                                                                                                                            | 63 |

| Tab. 10 Relative comparison of VSI losses for selected values of fixed d compared to optimized dead-time for various speed references and $R_{load} = 73 \Omega$ |    |

| Tab. 11 Dead-time optimization method comparison                                                                                                                 | 67 |

## Abbreviations

| 2DEG   | Two-Dimensional Electron Gas                      |

|--------|---------------------------------------------------|

| BEV    | Battery Electric Vehicle                          |

| CAN    | Controller Area Network                           |

| CCM    | Continuous Current Mode                           |

| DCM    | Discontinuous Current Mode                        |

| DFF    | Duty Feed Forward                                 |

| EV     | Electric Vehicle                                  |

| FOC    | Field Oriented Control                            |

| FR4    | Flame Retardant glass-reinforced epoxy resin      |

| GaN    | Gallium Nitride                                   |

| GIT    | Gate Injection Transistor                         |

| HEMT   | High Electron Mobility Transistor                 |

| ICE    | Internal Combustion Engine                        |

| IGBT   | Insulated Gate Bipolar Transistor                 |

| IMS    | Insulated Metal Substrate                         |

| LCO    | Lithium Cobalt Oxide battery                      |

| LFP    | Lithium Ferro Phosphate battery                   |

| LMO    | Lithium Manganese Oxide battery                   |

| LTO    | Lithium Titanate Oxide battery                    |

| LUT    | Look Up Table                                     |

| MCU    | Microcontroller                                   |

| MDmesh | Multiple Drain mesh                               |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| NCA    | (Lithium) Nickel Cobalt Aluminium battery         |

| NMC    | (Lithium) Nickel Manganese Cobalt battery         |

| PCB    | Printed Circuit Board                             |

| PFC    | Power Factor Correction                           |

| PHEV   | Plug-in Hybrid Electric Vehicle                   |

| PLL    | Phase Locked Loop                                 |

| PMSM   | Permanent Magnet Synchronous Motor                |

| PWM    | Pulse Width Modulation                            |

| RF     | Radio Frequency                                   |

| SiC    | Silicon Carbide                                   |

| SJ     | Super-Junction MOSFET                             |

| SVPWM  | Space-Vector Pulse Width Modulation               |

| TO-247 | Transistor Outline                                |

| VRB    | Vanadium Redox flow Battery                       |

| VSI    | Voltage Source Inverter                           |

| WoS    | Web of Science                                    |

|        |                                                   |

## Nomenclature

| $C_{oss}$                           | Output capacitance                                      |

|-------------------------------------|---------------------------------------------------------|

| D                                   | Converter duty cycle                                    |

| $D_{MCU}$                           | Microcontroller set duty cycle                          |

| $d_{a,} d_{b,} d_{c}$               | Duty cycle of phase a, b, c                             |

| d <sub>limit</sub>                  | Minimum duty cycle limit value                          |

| fsw                                 | Switching frequency                                     |

| gm                                  | Device transconductance                                 |

| $i_{a,ib,ic}$                       | Phase currents                                          |

| $i_{lpha,}i_{eta}$                  | Currents in $\alpha$ , $\beta$ plane                    |

| $i_{d,i_q}$                         | Currents in d, q plane connected with rotor             |

| <i>i</i> <sub>ch</sub>              | Channel current                                         |

| i <sub>in</sub>                     | Converter input current                                 |

| $i_{out}$                           | Half-bridge output current                              |

| ILtoff                              | Reverse inductor current during off time                |

| K                                   | Clarke's transformation coefficient                     |

| Р                                   | Converter operating power                               |

| Pcond                               | Transistor conduction losses                            |

| $P_d$                               | Dissipated power                                        |

| Pout                                | Converter output power                                  |

| $P_{sw}$                            | Transistor switching losses                             |

| R <sub>DSon</sub>                   | On-state resistance                                     |

| R <sub>epi</sub>                    | Epitaxial layer resistance                              |

| $R_{ch}$                            | Channel resistance                                      |

| R <sub>sub</sub>                    | Substrate resistance                                    |

| <b>R</b> <sub>thcs</sub>            | Case to substrate thermal resistance                    |

| <b>R</b> <sub>thsr</sub>            | Substrate to radiator thermal resistance                |

| <b>R</b> <sub>thjc</sub>            | Junction to case thermal resistance                     |

| $t_{d(rise)}, t_{d(fall)}$          | Delay time of the rising and falling edge of the driver |

| $t_{dt}$                            | Dead-time duration                                      |

| $t_{on}$                            | Transistor on time                                      |

| Т                                   | Switching period                                        |

| $V_{a,}V_{b,}V_{c}$                 | Phase voltages                                          |

| $V_{\alpha,}V_{\beta,}$             | Voltages in $\alpha$ , $\beta$ plane                    |

| $V_{d,}V_{q,}$                      | Voltages in d, q plane connected with rotor             |

| $V_{BR}$                            | Breakdown voltage                                       |

| V <sub>DC</sub>                     | Converter DC-link input voltage                         |

| $V_{DS}$                            | Drain to Source voltage                                 |

| V <sub>GS</sub>                     | Gate voltage applied from driver                        |

| V <sub>GS(th)</sub>                 | Gate threshold voltage                                  |

| V <sub>out</sub><br>V <sub>SD</sub> | Converter DC output voltage                             |

| ~                                   | Transistor reverse voltage                              |

| $V_{GS(off)}$                       | Gate driver negative voltage in off state               |

### **1** Introduction

Electric vehicles were popular at the end of the 19<sup>th</sup> and beginning of the 20<sup>th</sup> centuries [1]-[4]. They were easy to operate, immediately ready to ride compared to early combustion engine vehicles and were clean. When the internal combustion engine was improved and the fuel became cheap and available around the year 1920, electric vehicles with battery storage practically became extinct except golf carts [2].

A problem with early electric vehicles existed regarding the low energy density of their lead-acid batteries, storing about 0.3 % of the energy of petrol for a given mass. The result of the low energy density was very short range, limited only to the inner city. With the growth of urban zones people needed long range vehicles which the then-current battery technology could not support [5].

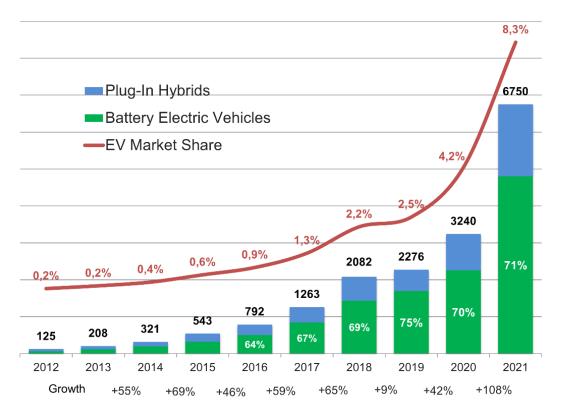

In recent years the development of lithium-based cells leads to new electric vehicles (EVs) appearing on the market. From 2010 to 2021 6.8 million EVs (including hybrid vehicles) were sold worldwide according to [6] presented in Fig. 1.

**EV** VOLUMES

#### GLOBAL BEV & PHEV SALES ('000s)

Fig. 1 Global EV sales [6]

Due to the emerging legislation and the growing societal demands in many countries worldwide, the requirements for the efficiency of electrical equipment are constantly increasing. This trend is also driven by the ongoing boom in electric mobility, where it is essential to achieve a high power density of the on-board and off-board electronic components. Therefore, in the field of power electronics and electric drives, significant effort is put into developing more efficient and compact devices and converters [7].

The design of small and highly efficient power converters for electric motors demands wide bandgap semiconductors such as those based on silicon carbide (SiC) and gallium nitride (GaN). Due to a significant reduction in switching losses, GaN-based transistors offer superior performance in high-frequency hard-switched converters than silicon transistors [8], [9]. For these advantages, they are started being used in electrical drives, too [10].

Within electrical drives, especially when powered by batteries, efficiency and power density are essential aspects. The design of small and highly efficient power converters for electric motor control demands wide bandgap semiconductors such as those based on SiC and GaN. These materials, with a high inner electric field, improve the transistor's parameters, such as the current density and on-state resistance. Furthermore, the low parasitic capacitances allow them to operate at higher switching frequencies than silicon devices [7], [8] and [9], [10]. Besides, GaN-based transistors have no reverse recovery charge due to the absence of the freewheeling diode. However, fast-switching devices also bring challenges to the circuit board design and control strategies [11].

The main motivation of this thesis is to analyse the problems that limits usage of GaN transistor in power converters and brings improvements resulting in GaN-based converters to be more efficient in the future.

#### **1.1 The State of Art**

#### 1.1.1 Hybrid Electric Vehicles

The hybrid vehicle contains both an internal combustion engine (ICE) and an electric motor. There are multiple options how to connect them. Hybrids are divided into series, parallel and series-parallel drive systems.

The series hybrid contains an ICE with a generator that charges batteries that supply the electric motor.

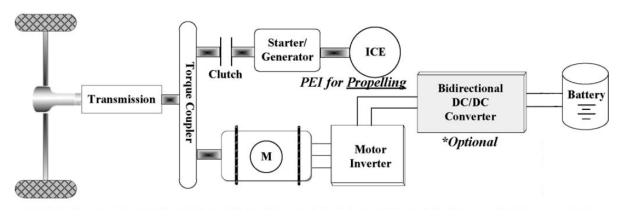

The parallel hybrid has both an ICE and an electric motor connected to the transmission.

By adding a rotary power splitter, the combination of both can be made.

The parallel hybrid topology is shown in Fig. 2. The optional bidirectional DC/DC converter between battery and motor inverter is implemented in case small capacity low voltage batteries are installed while the DC-bus voltage of the motor inverter is higher.

Fig. 2 Parallel hybrid vehicle topology [12]

#### 1.1.2 Battery Electric Vehicles

When we remove ICE completely from the vehicle and increase the battery capacity we can call it battery electric vehicle (BEV).

#### 1.1.2.1 Lithium-based Batteries

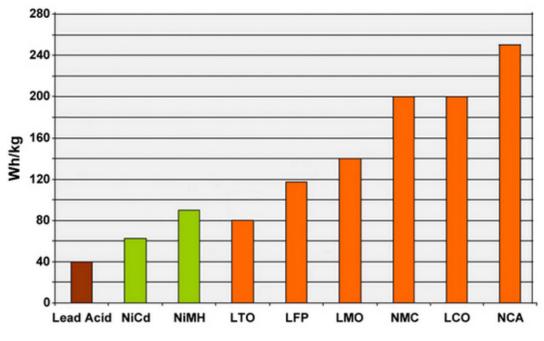

Due to the lithium cell's high energy density making the battery lightweight it is the mainstream type of traction battery today. A comparison of energy densities of multiple types of battery technologies [13] is shown in Fig. 3.

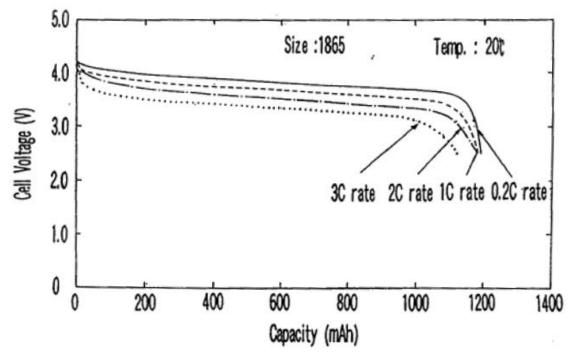

An example of the discharge curves for one cell is pictured in Fig. 4. The voltage remains relatively stable during discharge compared to previously used lead or nickelbased cells.

Fig. 3 Energy density comparison for lead, nickel and lithium-based cells [13]

Fig. 4 Discharge curve of lithium-based cell [14]

To increase the specific energy while keeping the cost low, traction batteries are currently made of a large number of series-parallel connected cylindrical cells. An example of a 500 Wh battery pack of lithium-based cells is shown in Fig. 5. The benefit of cylindrical cells is their mechanical stability and the fact that, due to common usage, they became more affordable.

Fig. 5 Example of 500 Wh battery pack of lithium cells

#### 1.1.2.2 Flow Batteries

The main difference from the batteries mentioned above is that the energy in the flow battery is not stored in the cell itself but in tanks of liquid electrolyte. The storage topology makes the flow battery easily scalable from small storages for off-grid houses to large scale on-grid energy storages [15].

The flow battery gives us two independent parameters by which to scale it. The battery's energy capacity is defined by the volume of the storage tanks for electrolyte and the power by the design of flow cells.

The active surface area of the cell's electrodes defines the maximum current, and the number of cells defines the battery voltage [16].

In the case of using a flow battery for an electric traction vehicle the energy density can outperform the lithium-based battery [17], [18]. A recently developed prototype of flow battery powered vehicle called QUANT 48VOLT by Nanoflowcell is achieving a range of 1600 km [19].

Liquid electrolyte stored in tanks gives the opportunity to charge the EV simply by pumping the discharged fluid out of the tanks, positive and negative separately, and pumping back a charged one as fast as refilling of petrol-fuelled cars is done.

The discharged electrolyte is put into another flow battery system to be recharged, for example, in large scale energy storage as part of a solar plant.

The energy is stored in different oxidation states of a given chemical, for example vanadium ions in the case of a vanadium redox flow battery (VRB). Since both positive and negative electrolytes are the same chemical, there is no degradation process in the electrodes [20]. The lack of degradation allows the flow battery to outperform the above mentioned technologies in lifespan. A large scale energy storage system for wind turbines

equipped with flow batteries is already reaching over 270 000 charge-discharge cycles [16].

In the flow battery energy is stored in tanks with liquid electrolyte. Positive and negative electrolytes are stored separately. The electrolyte is pumped through a pack of cells; charged electrolyte enters the cells and is returned to the tank in a discharged state. Due to mixing of the charged and discharged electrolyte, the cell voltage decreases during the discharge process. The interdependence of cell voltage and concentration of  $V^{2+}$  ions [20] is demonstrated in Fig. 7.

Fig. 6 Vanadium redox flow cell principle [20]

Fig. 7 Vanadium redox flow cell voltage [20]

The result is a significant difference between charged and discharged flow battery voltages compared to lithium-based batteries. The DC/DC converter has to stabilize the battery voltage to provide constant DC-bus voltage for the traction motor DC/AC converter.

Individual cells can be stacked in series to reach higher terminal voltage [21] while they share the same electrolyte that is pumped through them from the same tank as seen in Fig. 8 and Fig. 9. Increasing the number of cells increases the leakage current that goes through the liquid between cells that are at different potentials. The solution for leakage current is increased length of tubing with smaller diameter between cells however, generally speaking, the flow battery operates better at low voltage, for example 48 V, and high current depending on the needed power.

Fig. 8 Multiple cell vanadium redox flow battery [21]

Fig. 9 Vanadium redox flow battery stack [16]

#### 1.1.3 **Power Converters in Electric Vehicle Tractive System**

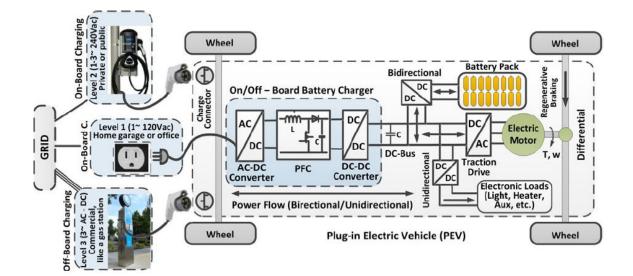

A typical diagram of the vehicle tractive system topology is shown in Fig. 10.

The traction battery is arranged as a series or series-parallel combination of cells that have a total voltage usually equal to the DC-bus voltage of the motor controller. These days regular EVs are using 400 V or 800 V. Optionally there can be a bidirectional converter placed between the battery pack and the DC-bus. This is often omitted to increase the system overall efficiency and the regulation is done in the motor converter. It means the motor is designed to utilize the available DC-link voltage equal to the battery.

Non-isolated boost converters are optionally present in vehicles with 800 V battery to enable them be fast-charged from 400 V DC chargers.

Isolated DC/DC converters are used in on-board chargers to provide the required safety. To decrease the amount of converters to reduce the amount of expensive power semiconductors, the charger can be made of a DC/AC traction converter and a motor winding according to [22]. On-board chargers are designed in range of power from 3.6 kW single phase to 11 kW or 22 kW three phase.

Unidirectional isolated DC/DC is used to supply the low-voltage on-board components. On-board grid usually operates on 12 V or 24 V. To reduce the losses in the wiring the on-board grid voltage can be also designed at 48 V. These converters are designed typically in 1 kW power range.

Fig. 10 EV power converters [22]

#### 1.1.4 Semiconductor Devices

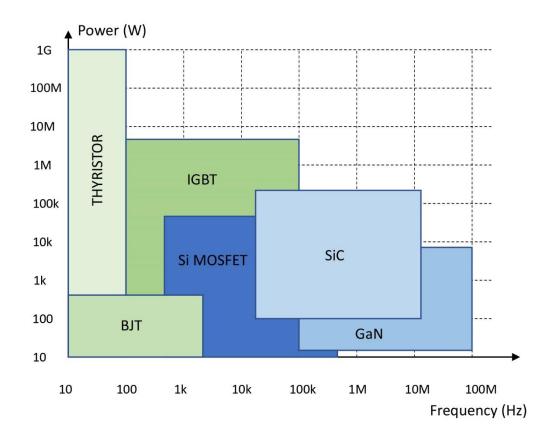

The following chapter focuses on the comparison of power semiconductors available for today's converter designs. Among the wide spectrum of different technologies on the market today, the following selection was chosen for comparison.

Fig. 11 Power semiconductors typical application for power and switching frequency [23]

#### 1.1.4.1 Si MOSFET

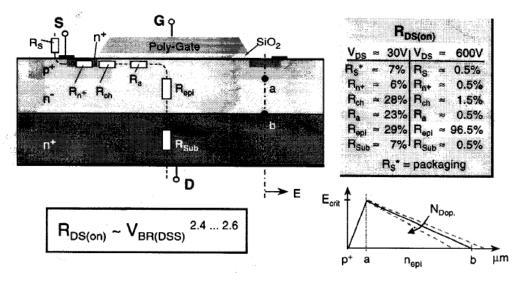

The technology of the classic metal oxide semiconductor field effect transistor (MOSFET) structure performs well at low voltages. For higher voltages the  $R_{DSon}$  rises rapidly [23]. Components of the  $R_{DSon}$  are shown in Fig. 12.

Fig. 12 Classic MOSFET structure R<sub>DSon</sub> components [23]

For higher voltages the  $R_{epi}$  becomes significant so other technologies were developed to reduce this resistance while keeping a high breakdown voltage  $V_{BR}$ .

Classic MOSFETs with  $V_{BR} = 100$  V reach very low  $R_{DSon}$  and are relatively cheap compared to other technologies. However, for higher voltages it is better to look for a different type of MOSFET structure, super-junction (SJ) such as CoolMOS for example.

Today's technology enables the thickness of the structure be thin while keeping the high breakdown voltages so the  $R_{epi}$  becomes least significant compared to the channel resistance  $R_{ch}$ .

#### 1.1.4.2 Si SJ MOSFET (CoolMOS)

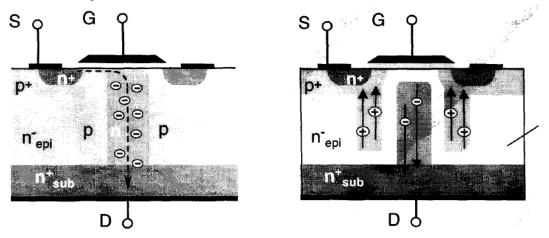

When trying to decrease the  $R_{DSon}$  of the classic MOSFET structure at higher breakdown voltages, the structure with vertical p-doped areas as shown in Fig. 13 was developed.

Due to the fact that only majority carriers conduct the current, switching losses remain the same as those of the classic structure while  $R_{DSon}$  is decreased even at high breakdown voltages.

Fig. 13 CoolMOS structure in turn-on (left) and turn-off state (right) [23]

CoolMOS technology now provides 10 times lower  $R_{DSon}$  compared to the classic MOSFET structure while keeping equal gate charge [24].

Switching losses equal those in classic MOSFETs so CoolMOS achieves higher efficiency in resonant converters compared to classic MOSFET structure just due to lower  $R_{DSon}$ .

#### 1.1.4.3 Si SJ MOSFET (MDmesh)

The multiple drain mesh (MDmesh) structure shown in Fig. 14 appeared in 2000 and is in its fifth generation, achieving one of the lowest  $R_{DSon}$  values in the field of Si MOSFETs [25]. When developed, this technology decreased the conduction losses per area to 50 % compared to regular Si MOSFETs [26]. MDmesh allows transistors of half the conventional die size, giving 50 % lower gate charge for applications of the same power.

This technology makes a good alternative to CoolMOS that is, due to lower output capacitance, more suitable for hard-switching applications.

Fig. 14 MDmesh structure [26]

#### 1.1.4.4 Si IGBT

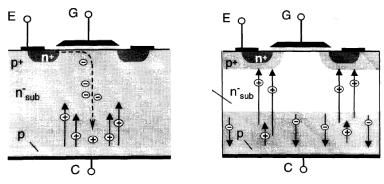

Unlike in MOSFETs, insulated gate bipolar transistor (IGBT) structure needs a significant voltage drop of 0.7 V when turned-on to increase the concentration of charge carriers in the drift zone to provide conductivity. Due to the voltage drop, the drift zone is filled with both electrons and holes which cause a tail current when turned-off. Because of this tail current, IGBTs have higher turn-off switching losses compared to MOSFETs [23]. The structure is shown in Fig. 15.

Fig. 15 IGBT structure in turn-on (left) and turn-off (right) [23]

IGBT transistors are still very popular in high power converters in the 1.2 kV voltage range. High switching losses associated with IGBT turn-off tail current are reduced by decreasing the switching frequency.

When high frequency is needed in high voltage applications the better option presently is the SiC MOSFET.

#### 1.1.4.5 SiC

Silicon carbide (SiC) based semiconductors are real competitors for IGBT transistors in high power, high voltage converters [27]. The device to device comparison according to [30] is shown in Tab. 1.

| Tab. 1 SiC to IGB1 converter enciency comparison [50] |                 |                 |  |

|-------------------------------------------------------|-----------------|-----------------|--|

|                                                       | IGBT system     | SiC system      |  |

| Conduction loss                                       | IGBT 114W       | MOSFET 36W      |  |

| (per device)                                          | Diode 20W       | Diode 25W       |  |

| Switching loss (per                                   | 164W            | 36W             |  |

| device)                                               |                 |                 |  |

| Inverter total loss                                   | 1789W           | 584W            |  |

| Output power                                          | 61.2kW          | 61.2kW          |  |

| Efficiency                                            | $\eta = 97.1\%$ | $\eta = 99.1\%$ |  |

Tab. 1 SiC to IGBT converter efficiency comparison [30]

SiC as a MOSFET structure has lower conduction losses compared to IGBT but the significant difference is in switching losses.

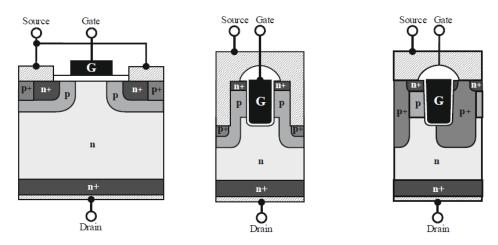

SiC MOSFET structure is close to the classic Si MOSFETs as shown in Fig. 16. The proposed asymmetric structure in [31] with better channel mobility decreases the on-resistance while the deep p-wells provide the function of freewheeling diode.

Fig. 16 SiC MOSFET classic structure (left), trench structure (center), proposed improved asymmetric trench structure (right) [31]

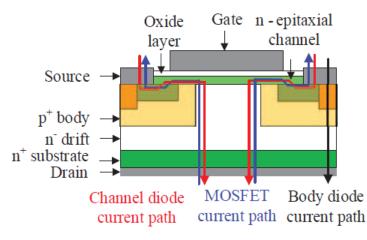

To improve the freewheeling diode characteristics, an external SiC Schottky barrier diode can be added to provide fast switching while the slower body diode conducts the current after the completion of the switching transition because the body diode has lower on-resistance [32].

Fig. 17 External Schottky diode in SiC transistor [32]

The main negative aspect of SiC technology is its cost which is now about 5 times that of a Si IGBT module of the same rated voltage and current. Due to the cost, SiC technology is limited to use in a specific range of converters where high power density is required, such as traction converters for electric vehicles. However small power 650 V SiC transistors have recently appeared and are available in similar packaging and in the same price range as IGBT or Si MOSFETs and, promising to operate with standard drivers, will be great competitors to Si transistors.

#### 1.1.4.6 GaN

High-electron mobility transistors (HEMT) based on gallium nitride (GaN) in recent years have appeared in the power electronics field [28], [29]. Earlier depletion-mode GaN transistors have been used in RF applications. For power electronics the enhancementmode is needed so multiple ways to obtain it have been developed.

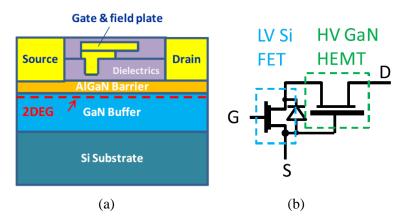

Similar to early SiC technology, the cascade topology has been applied [28] to high voltage depletion-mode GaN structures on Si substrates to produce enhancement-mode devices as shown in Fig. 20. The lateral structure provides low channel resistance due to the existing 2-D electron gas (2DEG) formed by strong polarization in the GaN layer. Normally, to deplete this region a negative gate voltage must be applied. The cascade topology simply adds a classic Si MOSFET transistor in series with the source electrode to obtain the required negative gate bias during turn off.

Fig. 18 Depletion mode GaN on Si (a) as a part of the cascade (b) [7]

The main problem of the cascade connection is increased on-resistance because of two channels being in series.

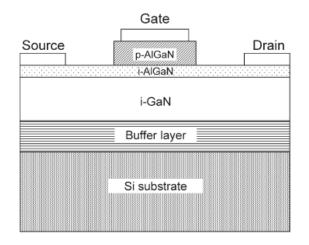

To produce an enhancement mode GaN transistor, the gate threshold voltage Vth needs to be increased. Using the p-doped layer under the gate, the channel is depleted when no voltage is applied to the gate [33]. Such a transistor is called gate injection transistor (GIT) whose structure is shown in Fig. 19.

When a positive voltage higher than Vth is applied on the gate electrode, hole injection from the p-doped layer under the gate enables the channel to conduct current with  $R_{DSon}$  similar to that of a normally-on GaN structure.

Fig. 19 GaN on Si GIT structure [33]

The main benefit of the GaN transistor structure is the reverse conduction region. The reverse characteristic is able to perform as a freewheeling diode in classic converter applications. Since there is no substrate diode, this transistor has no reverse recovery charge. While the reverse on-state resistance is controlled by positive gate voltage, the structure conducts reverse current even with zero gate voltage [34].

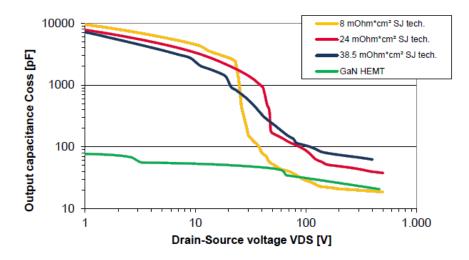

The GaN structure offers linear change in output capacitance during turn-on/off compared to Si or SiC [8], as it is depicted in Fig. 20.

Fig. 20 Output capacitance dependence on  $V_{DS}$  [8]

The output capacitance linearity is important for converter efficiency at high frequencies. The mechanical design of the converter limits the maximum di/dt capability and output capacitance linearity makes the di/dt slew rate constant during the whole process of turn-on and turn-off.

According to [35] the GaN transistor has approximately 10 times less gate charge compared with Si MOSFETs chosen for converters of the same power category. On the other hand, the gate driver must be fast enough for the transistor to work at high frequencies where the above described benefits become useful.

Si, SiC and GaN technologies are compared in Tab. 2 in [8] with selected transistors being of the same power range.

| _                            | Silicon        | SiC           | GaN        |

|------------------------------|----------------|---------------|------------|

| Concept                      | super junction | planar MOSFET | eMode HEMT |

| Blocking voltage             | 600V           | 900V          | 600V       |

| On-state resistance (typ.)   | 56 mOhm        | 65 mOhm       | 55 mOhm    |

| Reverse recovery charge      | 6000 nC        | 130 nC        | 0 nC       |

| Energy stored in Coss @ 400V | 8.1 μJ         | 8.8 µJ        | 6.4 μJ     |

| Charge stored in Coss @ 400V | 420 nC         | 70 nC         | 40 nC      |

| Turn-off loss @ 10A / 400V   | 15 μJ          | 10 µJ         | 10 µJ      |

Tab. 2 Si, SiC and GaN transistor parameter comparison [8]

The main trouble remaining is that the available parts suit relatively small power converters only in the range of a few kW. Compared to SiC the base material is cheaper so GaN has the potential to replace Si transistors in the future.

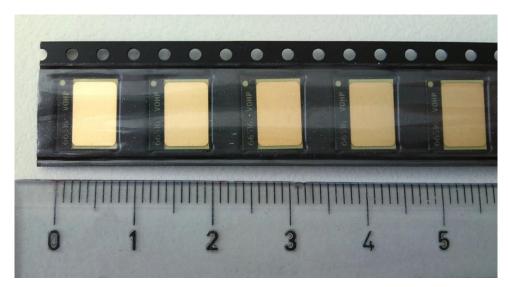

In Fig. 21 currently available GaN transistors are shown.

Fig. 21 GaN-based 650 V 60 A transistors

#### **1.2 Motivation**

During my bachelor and master studies I was interested in electric vehicle tractive system and gained some experience when designing and testing an IGBT based DC/DC converter for a separately excited DC traction motor in Citroën Berlingo Electrique. Utilizing the new generation IGBT enabled to increase the vehicle tractive converter efficiency significantly which resulted in a small fully air-cooled design.

At the time I entered the doctoral studies, new SiC and GaN-based semiconductors were entering the field of power electronics suggesting new possibilities in efficiency improvement and power density increase. Based on previous interest in electric vehicles the framework topic "Analysis of Power Electronic System of Electric Vehicle with Energy Storage" was chosen.

Based on the stated thesis objectives the thesis title "Improving the Electric Vehicle Converter Performance Using New Semiconductor Components" was adopted. It represents a concretization of the original framework topic.

#### **1.3** Thesis Objectives

Based on the state of the art and discussed problems the global objective has been defined as minimizing losses in GaN-based converters. To succeed this global objective, the following five thesis objectives were taken into account.

#### **1.** Improving drivers' performance to maximize utilizing the devices' capability.

The idea is to create a fast driver that will ensure safe operation of the GaN transistor in power converters when utilizing fully the transistor operation area. This leads to the fast current limiting driver development that will respect specific behaviour of fast switching GaN transistors.

#### 2. Analysing the new perspective devices' cooling possibilities.

Analysis of the new cooling possibilities in comparison with regularly used means of cooling needs to be done with respect to the new design of GaN devices. Their high current density brings challenges in the cooling system design for transistors with small packages.

## 3. Minimizing the new devices' losses in their switch-on state by the software control algorithm extension only.

Analysing software possibilities that will optimize the switch-on state performance of the GaN transistor in respect to the dynamic behaviour of the on-state resistance. The dynamic resistance, especially current-collapse phenomenon present in HEMT devices needs to be studied.

## 4. Minimizing the new devices' losses in their switch-off state by the software control algorithm extension only.

Analysis of switch-off state behaviour of GaN transistor and its losses that significantly decrease the performance of HEMT devices when operated in reverse conduction region. This leads to a development of an algorithm that tracks the optimum dead-time to minimize the time of high reverse voltage drop operation.

## 5. Reducing the converters' output voltage drop by the on-line dead-time control.

Dead-time in converters' half-bridge causing voltage drop can be reduced by optimum dead-time setting. However, the optimum dead-time changes due to transistors' switching delays are current depending. A software on-line control based on actual measured half-bridge current can improve the overall efficiency curve of AC converters.

### 2 Current Limiting Driver for GaN Transistor

This chapter was partly published in Proceedings of the 2017 International Conference on Applied Electronics, see [39].

The quickly developing technology of GaN power transistors is calling for a new sophisticated high speed driver. The fast switching GaN transistors with no reverse recovery charge allows us to design a new level of high frequency converters with high efficiency and power density. Together with the transistors we have to keep improving other components to meet their requirements. One key component is the gate driver this chapter is dealing with.

The goal of the driver is to operate the transistor within the whole range of its parameters. High speed current limiting driver was described in [40] for SiC transistors but GaN transistor has the potential to operate at higher frequencies and therefore the driver should be even faster.

For most types of converters, the main benefit of the increased operating frequency is increasing the power density. The higher the frequency, the smaller inductance is needed. Thereafter the inductors' cores can be smaller and number of turns lower, which means that the conductivity losses in copper are substantially reduced and the efficiency significantly increased.

For off-grid operating inverters, the output short circuit or time limited overload is common and the converter has to handle it without troubles. These high efficiency converters provide very low output impedance compared to the grid which causes much higher short-circuit currents. The driver has a possibility to be able to turn off the transistor safely when the maximum allowed drain current value is being exceeded.

#### 2.1 Gallium Nitride Basis

#### 2.1.1 No Reverse Recovery

GaN transistor does not contain parasitic substrate free-wheeling diode compared to Si or SiC MOSFETs. Nevertheless, GaN transistor allows reverse conduction without reverse recovery charge. Reverse conduction is used after turning-off the opposite transistor in the half-bridge, as illustrated in Fig. 22.

In reverse conduction the positive gate voltage can be applied to reach low switchedon state resistance. When looking into datasheets of today's available GaN transistors [34], the channel resistance in reverse conduction can substitute the freewheeling diode, see Fig. 23. In this case the conduction losses are not higher compared to other switching devices.

Fig. 23 Reverse conduction region [34]

#### 2.1.2 **Gate Driving Requirements**

The GaN transistor has approximately 10 times lower gate charge compared to Si MOSFET of the same power category [8]. The gate threshold voltage depends on the technology. The E-mode HEMT forward characteristic example is shown in Fig. 24.

More important is to choose a driver operable at the desired frequency. Propagation delays of the driver output stage are now important because they cause pulse width modulation (PWM) signal distortion when on and off delays are not equal.

In datasheets some MOSFET drivers are labelled as ultrafast [41], but unfortunately nowadays they became too slow for GaN transistors and the driver is actually the part that limits the maximum PWM frequency.

Fig. 24 Forward conduction region [34]

#### 2.2 GaN Driver Design Requirements

#### 2.2.1 Current Measuring

The method of measuring the transistor's on-state resistance voltage drop has been chosen to determine the current value. The on-resistance  $R_{DSon}$  is a temperature dependent quantity defined in the datasheet, so it can be used for calculation of the allowed maximum voltage drop across the drain-source channel. The  $R_{DSon}$  temperature dependency varies with the transistor's technology, for an example see Fig. 25.

The calculated maximum voltage drop is then set as a reference for fast comparator that is measuring the voltage to determine the maximum current allowed.

The pulse by pulse current limiting consists of RS flip-flop, so the transistor remains turned off until the next rising edge of the input signal is received. However, the controller receives the error signal and it depends on the controller only if the next rising edge will come.

The output stage of the driver is equipped with a high speed tri-state buffer controlled according to the Tab. 3.

Fig. 25 R<sub>DSon</sub> temperature dependency [34]

| Tab. 3 Gate control logic |              |               |  |

|---------------------------|--------------|---------------|--|

| <b>PWM</b> Input          | Over-current | Gate output   |  |

|                           | detected     |               |  |

| 0                         | Х            | Off           |  |

| 1                         | 0            | On            |  |

| 1                         | 1            | Slow turn off |  |

#### 2.2.2 Safe Turn-Off Over-Current

The bigger the current the higher is the di/dt during turning off when the fall time determined by the gate resistor does not change. High di/dt is causing overvoltage spikes on the parasitic inductances in the circuit. To prevent the damage of the transistor during turning off the over-current state the gate is discharged through an extra path with higher gate resistance compared to normal turn-off. Higher gate turn-off resistance is discharging the gate slower which causes the transistor to turn off slower, reducing the di/dt.

Fig. 26 compares the desired turn off with the one caused by the driver delay.

The threshold current is set to reasonable value but the peak current will be higher due to the propagation delay of the driver.

Compared to Si IGBT and SiC where this method is also used [40], the turn-off delay of the driver itself is significant. GaN is much faster, even compared to today's IC drivers. The delay from the over-current detection till the actual beginning of turning off has to be considered.

Fig. 26 Fall time extending

#### 2.2.3 PCB Design

The path that consist of the low side transistor, high side transistor, and DC-link capacitor has to be designed with the lowest possible parasitic inductance.

Parasitic inductances in the path are causing voltage spikes during the transistors' switching on and off. The printed circuit board (PCB) design methods how to decrease this problem and utilize the voltage and current capability of the transistor are described for example in [42].

A basic one is to connect the path on the PCB using short but wide polygons instead of thin and long paths. Multiple layer board allows to cancel most of the inductance when routing the path in a different layer the opposite direction creating a parasitic inductor with a minimum area. This leads to the design where the DC-link capacitor is placed inline with the half-bridge transistors [43].

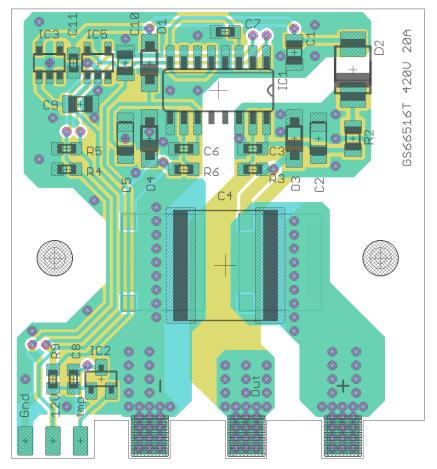

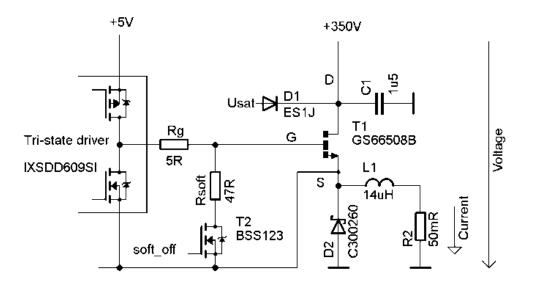

An example of the GaN half-bridge board design is in Fig. 27 where the transistors are placed on the bottom side right below the temperature-stable ceramic (C0G) DC-link capacitor. This board was designed for the converter in chapter 6.

Fig. 27 Current loop minimizing example

# 2.3 Designed Prototype

Based on the requirements of GaN transistors a new driver circuit have been designed.

## 2.3.1 **Proposed Driver Schematic Diagram**

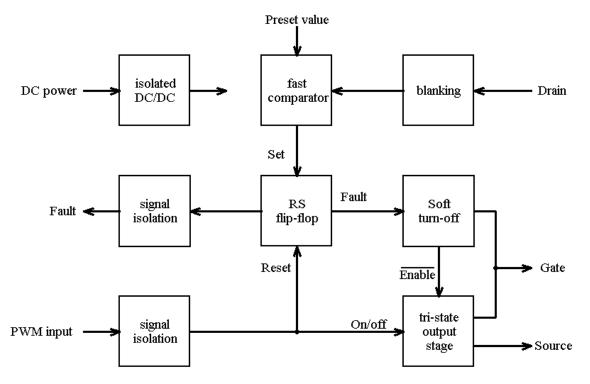

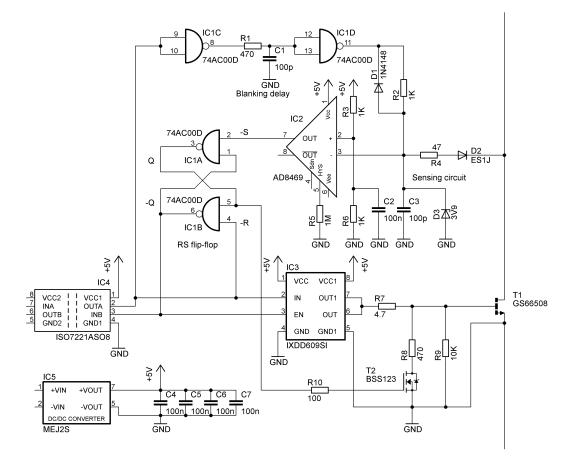

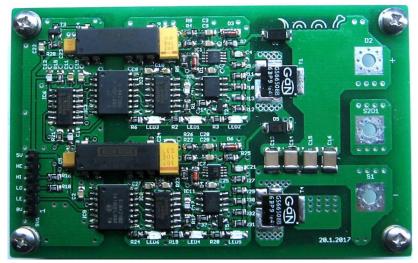

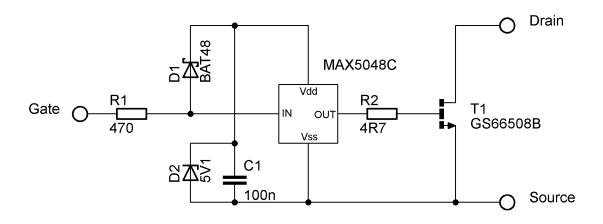

In Fig. 28 a block diagram of one side of the half-bridge driver is described. The detailed schematic diagram is in Fig. 29.

The isolation barrier is equipped with bidirectional isolators for input PWM signal and fault output. A DC/DC converter provides the power for logic and output stage of the driver, too. Both low and high sides have their own isolators and DC/DC isolated converters.

The PWM signal feeds directly the output tri-state buffer that controls the gate in normal operation.

Fig. 28 Block diagram of the current limiting driver

Fig. 29 Circuit diagram of the current limiting driver

### Current Limiting Driver for GaN Transistor

Current is measured using a voltage drop across the transistor which is sampled through a diode. Sampling circuit is necessary to measure the low voltage only when transistor is turned on. It also adds a small delay that respects the propagation delay of the signal path so that the comparator doesn't receive a false voltage before the transistor is turned on.

Fast comparator has a pre-set value of maximum drain to source voltage and when the measured value is higher the output fault signal is set.

Fault signal changes the state of the RS flip-flop in the way that the output stage is forced to high impedance and gate is discharged through an extra path with a higher gate resistance to achieve the desired over-current soft turn off.

## 2.3.2 **Testing the Prototype**